Alhambra II FPGA

GH Wiki

FPGA development board (iCE40HX4K-TQ144 from lattice)

PCF File

https://github.com/FPGAwars/icestudio/blob/develop/app/resources/boards/alhambra-ii/pinout.pcf

Programming language

Related

Tools

DONE

Icestudio

GitHub

Frontend for

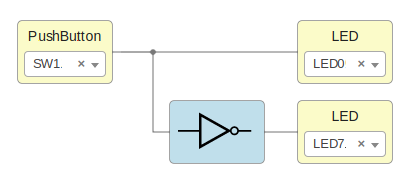

It's a great way to build little circuits to get a feeling for the FPGA. For example the following circuit will light LED 0 if the button 1 is pushed, otherwise LED7 would be the one active.

Might be necessary to launch it as root (with

sudo).Icestudio files are encoded in JSON.

Can be used to export verilog code

Tests

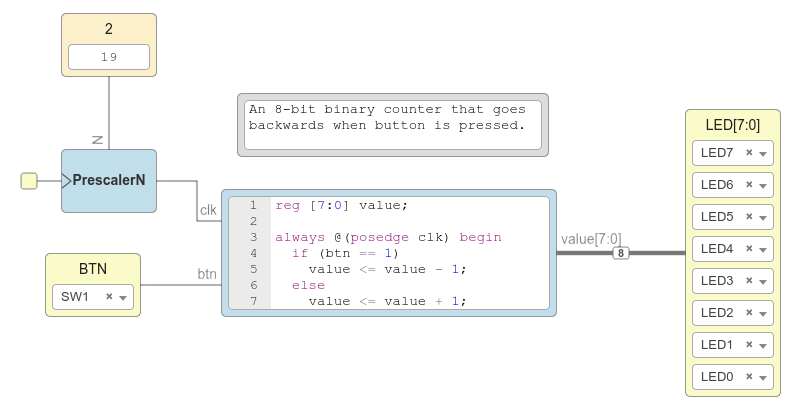

Count forward and backwards

// Code generated by Icestudio 0.5.0

// Mon, 22 Mar 2021 22:15:57 GMT

`default_nettype none

module main #(

parameter v2fb628 = 19

) (

input vaef181,

input vclk,

output [7:0] v31451a

);

localparam p1 = v2fb628;

wire [0:7] w0;

wire w2;

wire w3;

wire w4;

assign v31451a = w0;

assign w3 = vaef181;

assign w4 = vclk;

v6a5074 #(

.v100e1b(p1)

) vbb0b73 (

.v2efea4(w2),

.v0daa9e(w4)

);

main_v243a90 v243a90 (

.value(w0),

.clk(w2),

.btn(w3)

);

endmodule

module v6a5074 #(

parameter v100e1b = 22

) (

input v0daa9e,

output v2efea4

);

localparam p2 = v100e1b;

wire w0;

wire w1;

assign v2efea4 = w0;

assign w1 = v0daa9e;

v6a5074_vac7386 #(

.N(p2)

) vac7386 (

.clk_out(w0),

.clk_in(w1)

);

endmodule

module v6a5074_vac7386 #(

parameter N = 0

) (

input clk_in,

output clk_out

);

//-- Number of bits of the prescaler

//parameter N = 22;

//-- divisor register

reg [N-1:0] divcounter;

//-- N bit counter

always @(posedge clk_in)

divcounter <= divcounter + 1;

//-- Use the most significant bit as output

assign clk_out = divcounter[N-1];

endmodule

module main_v243a90 (

input clk,

input btn,

output [7:0] value

);

reg [7:0] value;

always @(posedge clk) begin

if (btn == 1)

value <= value - 1;

else

value <= value + 1;

end

endmodule

TODO

SymbiFlow

Homepage

TODO

Icestorm

Homepage

TODO

APIO

Environment/package collection for open FPGAs

Used by

Given a Verilog file, like Count forward and backwards

It can be sent to a FPGA with

apio build -b alhambra-iiIf normal

apiodoesn't generate files, try with the one on Icestudio's venv

TODO

Yosys

Homepage

Open synthesis suite